Supporting program

The top-class supporting program at electronica, which focuses on knowledge transfer and professional exchange, also shows what moves the industry.

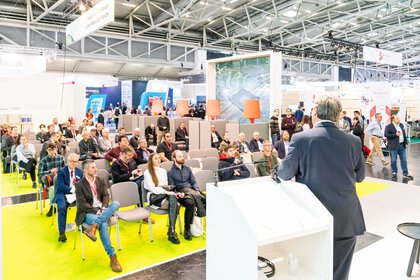

Forum events

The various electronica forums will deal with practical lectures on topics such as automotive, cyber security, printed electronics, embedded systems, IIoT, connectivity, printed circuit boards, power electronics, components, measurement technology and sensors. But also start-ups and ethical topics in electronics find their stage at our forums.

edge lab LIVE

New in 2026: edge lab LIVE is an exhibition area at electronica dedicated to edge computing. Technical executives, system architects, engineering managers, and embedded and application developers come together here to explore specific application scenarios for open-source and standard technologies.

Startups

With agile mindsets, innovative ideas and unconventional methods, startups are bringing new energy to the industry, and electronica offers them a stage. Young, up-and-coming companies will meet investors, buyers and potential partners at pitches, presentations and workshops. This is where cooperations begin that develop a special dynamic in the cooperation between the startup spirit and the structures of established companies.

Awards

Our awards pit the best of the best against each other. In exciting competitions and pitches, entrants showcase their innovation and full potential.

Careers

As a highly dynamic industry, electronics offers the best career opportunities for talents individuals. At electronica, they can take a look at the variety of offers, get to know job profiles, hold personal talks with top employers and concretize career plans. As an industry of the future, the electronics industry needs the best minds—and meets them at electronica.

CEO Roundtable

The CEO Roundtable is a highlight of electronica. Top international decision-makers discuss megatrends and the future of the electronics industry, global challenges and upcoming transformation processes. The exchange of experiences between the company leaders provides strategic insights, visionary considerations and concrete approaches to solutions for the central issues of our time.

electronica Automotive Conference

The electronica Automotive Conference features a comprehensive program that highlights the latest challenges and innovations in electronics and future mobility solutions. The conference provides a platform for exchange among leading experts from the international automotive and electronics industries. For the first time this year, the conference will be part of IAA MOBILITY as an integrated trade event.